Dip-switches¶

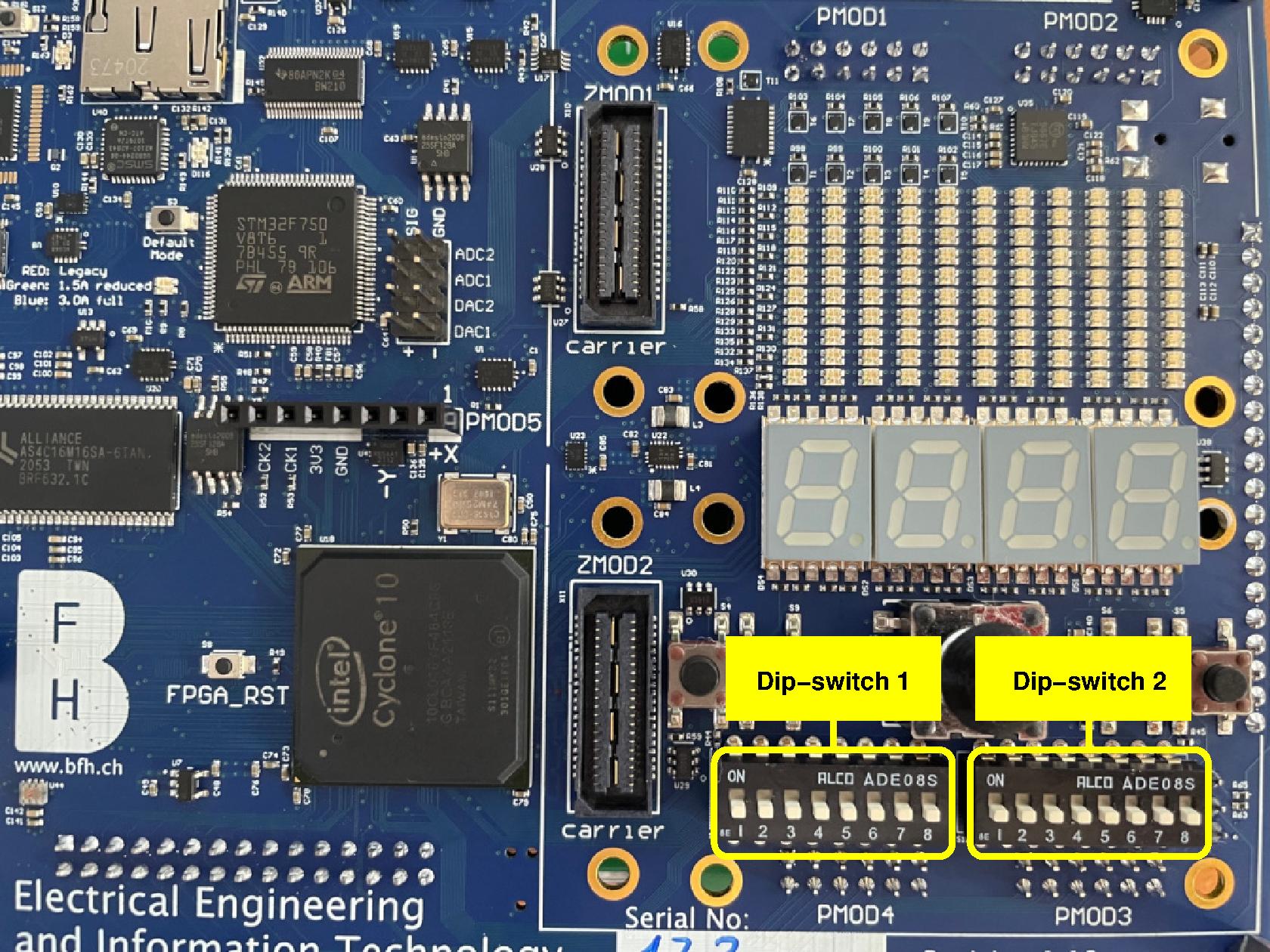

The leguan provides two 8-positions dip-switches:

Important

All the dip-switches are active low, meaning that when they are in position on they will provide a logic level 0, and when they are in position off, they give a logic level 1. Furthermore, all of them require an FPGA-IOB pull-up resistor to function correctly!

Dip-switch 1¶

The table below shows the pins on which the positions of the dip-switch are connected on the FPGA:

Name: |

FPGA pin: |

requires pull-up: |

|---|---|---|

position 1 |

PIN_V2 |

Yes |

position 2 |

PIN_V1 |

Yes |

position 3 |

PIN_U2 |

Yes |

position 4 |

PIN_U1 |

Yes |

position 5 |

PIN_T3 |

Yes |

position 6 |

PIN_F20 |

Yes |

position 7 |

PIN_R2 |

Yes |

position 8 |

PIN_R1 |

Yes |

Below you find the snippets on how to use these buttons in your toplevel.

Dip-switch 2¶

The table below shows the pins on which the positions of the dip-switch are connected on the FPGA:

Name: |

FPGA pin: |

requires pull-up: |

|---|---|---|

position 1 |

PIN_P3 |

Yes |

position 2 |

PIN_P2 |

Yes |

position 3 |

PIN_P1 |

Yes |

position 4 |

PIN_N2 |

Yes |

position 5 |

PIN_N1 |

Yes |

position 6 |

PIN_M3 |

Yes |

position 7 |

PIN_M2 |

Yes |

position 8 |

PIN_M1 |

Yes |

Below you find the snippets on how to use these buttons in your toplevel.

Using the dip-switches¶

In this section you find a VHDL top-level entity and the corresponding tcl-file that you can use to use the dip-switches.

Important

Although VHDL is case-insensitive, the tcl-files are not. Meaning that the port-names in the top-level entity need to be copied exactly in the tcl-files.

An example for a VHDL top-level entity is shown below:

library ieee;

use ieee.std_logic_1164.all;

entity leguanToplevel is

port ( dipSwitch1_b : in std_logic_vector( 7 downto 0));

end leguanToplevel;

To connect the above dip-switch to the correct pins of the FPGA, following tcl-script can be used:

set_location_assignment PIN_V2 -to dipSwitch1_b[7]

set_location_assignment PIN_V1 -to dipSwitch1_b[6]

set_location_assignment PIN_U2 -to dipSwitch1_b[5]

set_location_assignment PIN_U1 -to dipSwitch1_b[4]

set_location_assignment PIN_T3 -to dipSwitch1_b[3]

set_location_assignment PIN_F20 -to dipSwitch1_b[2]

set_location_assignment PIN_R2 -to dipSwitch1_b[1]

set_location_assignment PIN_R1 -to dipSwitch1_b[0]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[7]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[6]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[5]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[4]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[3]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[2]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[1]

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[0]

Note

The suffix

_bto the port name. This is general practice to indicate an active-low signal.The

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to dipSwitch1_b[7]line in the tcl-script. This instructs quartus to activate the FPGA pull-up resistor in the IOB. If this line would be omitted, theposition 1of the dip-switch does not function. The reason for this is that in case theposition 1is in the off position, the input is floating.Position 1of the dip-switch is the MSB of the vector, andposition 8of the dip-switch is the LSB of the vector.In

VHDLa bit of a vector is selected using round brackets, e.g.dipSwitch1_b(7). In the tcl-script, however, you have to use square brackets, e.g.dipSwitch1_b[7].

Hint

To activate the assignments, following steps need to be taken in quartus:

Go to

Tools->Tcl scripts....Add the

tclscript to your project by pressing the ButtonAdd to Project....Highlight the

tclscript by clicking on it in theLibraries:window.Press the

Runbutton.